集成電路行業(yè)專題 先進(jìn)制程貼近極限,Chiplet迎來黃金發(fā)展期

隨著全球半導(dǎo)體產(chǎn)業(yè)持續(xù)演進(jìn),摩爾定律的物理與經(jīng)濟(jì)效益雙重挑戰(zhàn)日益凸顯,單純依靠制程微縮提升芯片性能的路徑正逐漸逼近極限。在這一背景下,Chiplet(芯粒)技術(shù)以其靈活、高效、降本的優(yōu)勢,正成為延續(xù)摩爾定律、驅(qū)動(dòng)產(chǎn)業(yè)創(chuàng)新的關(guān)鍵范式,有望迎來黃金發(fā)展期。

一、先進(jìn)制程的極限挑戰(zhàn)與成本困境

傳統(tǒng)上,通過不斷縮小晶體管尺寸來提升芯片性能、降低功耗和成本的“摩爾定律”驅(qū)動(dòng)了半導(dǎo)體行業(yè)數(shù)十年的高速發(fā)展。當(dāng)制程節(jié)點(diǎn)進(jìn)入5納米、3納米乃至更先進(jìn)領(lǐng)域時(shí),技術(shù)復(fù)雜度呈指數(shù)級(jí)上升,導(dǎo)致研發(fā)與制造成本急劇攀升。物理極限如量子隧穿效應(yīng)、熱耗散問題等開始嚴(yán)重制約晶體管尺寸的進(jìn)一步微縮。這使得單一芯片的性能提升速度放緩,而單位晶體管成本下降的趨勢也出現(xiàn)逆轉(zhuǎn)。對(duì)于大多數(shù)應(yīng)用場景而言,追求最尖端制程已不再是性價(jià)比最優(yōu)的選擇,行業(yè)亟需新的技術(shù)路徑來平衡性能、功耗、成本和開發(fā)周期。

二、Chiplet:破局之道與核心優(yōu)勢

Chiplet技術(shù)通過將大型單芯片(SoC)拆分為多個(gè)功能、工藝可獨(dú)立的小芯片(芯粒),并利用先進(jìn)封裝技術(shù)(如2.5D/3D封裝、硅中介層等)進(jìn)行異構(gòu)集成,從而構(gòu)建出高性能的系統(tǒng)級(jí)芯片。這一模式的核心優(yōu)勢在于:

- 設(shè)計(jì)靈活性提升:允許混合使用不同制程、不同材料甚至不同廠商的芯粒,實(shí)現(xiàn)“最佳工藝做最適合的事”。例如,CPU核心可采用先進(jìn)制程以追求高性能,而I/O、模擬模塊等則可使用成熟制程以降低成本。

- 開發(fā)周期與成本優(yōu)化:芯粒可以復(fù)用已驗(yàn)證的成熟IP模塊,大幅縮短芯片設(shè)計(jì)周期,降低研發(fā)風(fēng)險(xiǎn)和成本。對(duì)于復(fù)雜芯片,尤其是大規(guī)模計(jì)算芯片(如CPU、GPU、AI加速器),Chiplet能有效分?jǐn)偢甙旱牧髌杀尽?/li>

- 性能與能效突破:通過3D堆疊等封裝技術(shù),可以大幅縮短芯粒間互連距離,實(shí)現(xiàn)超高帶寬和低延遲的數(shù)據(jù)傳輸,從而突破傳統(tǒng)單芯片在內(nèi)存帶寬和互連效率上的瓶頸,提升整體系統(tǒng)性能與能效。

三、產(chǎn)業(yè)生態(tài)加速成熟,黃金發(fā)展期已至

推動(dòng)Chiplet發(fā)展的關(guān)鍵要素正快速匯聚:

- 標(biāo)準(zhǔn)與接口統(tǒng)一:UCIe(Universal Chiplet Interconnect Express)等產(chǎn)業(yè)聯(lián)盟的成立和標(biāo)準(zhǔn)發(fā)布,為不同廠商芯粒的互連提供了開放、標(biāo)準(zhǔn)化的基礎(chǔ),是構(gòu)建健康產(chǎn)業(yè)生態(tài)的核心前提。

- 封裝技術(shù)革新:臺(tái)積電的CoWoS、英特爾的EMIB/Foveros、三星的X-Cube等先進(jìn)封裝技術(shù)不斷迭代,為Chiplet提供了可靠的物理實(shí)現(xiàn)基礎(chǔ)。

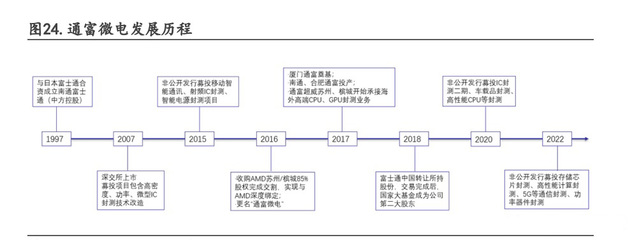

- 巨頭引領(lǐng)與全產(chǎn)業(yè)鏈布局:AMD、英特爾、蘋果等頭部廠商已在多款產(chǎn)品中成功應(yīng)用Chiplet設(shè)計(jì),證明了其商業(yè)價(jià)值。從EDA工具、IP供應(yīng)商、芯片設(shè)計(jì)公司到封裝測試廠,全產(chǎn)業(yè)鏈都在積極投入,生態(tài)日趨完善。

- 應(yīng)用需求驅(qū)動(dòng):在人工智能、高性能計(jì)算、數(shù)據(jù)中心、自動(dòng)駕駛等對(duì)算力需求爆炸式增長的領(lǐng)域,Chiplet是滿足其超高算力、高帶寬內(nèi)存需求的關(guān)鍵技術(shù)路徑。

四、投資視角:關(guān)注產(chǎn)業(yè)鏈核心環(huán)節(jié)

對(duì)于投資管理而言,Chiplet技術(shù)的興起將重塑集成電路產(chǎn)業(yè)的價(jià)值鏈,并催生新的投資機(jī)遇。建議關(guān)注以下核心環(huán)節(jié):

- 先進(jìn)封裝與測試:Chiplet的實(shí)現(xiàn)高度依賴于先進(jìn)封裝技術(shù),相關(guān)設(shè)備、材料及封裝測試服務(wù)供應(yīng)商將直接受益于需求增長和技術(shù)升級(jí)。

- EDA與IP供應(yīng)商:支持Chiplet架構(gòu)設(shè)計(jì)、仿真和驗(yàn)證的EDA工具,以及可復(fù)用的高性能芯粒IP,其戰(zhàn)略價(jià)值將進(jìn)一步提升。

- 具備Chiplet設(shè)計(jì)能力的芯片公司:特別是在高性能計(jì)算、AI、服務(wù)器等領(lǐng)域率先采用并掌握Chiplet設(shè)計(jì)能力的公司,有望構(gòu)筑新的技術(shù)壁壘和競爭優(yōu)勢。

- 接口技術(shù)與中介層供應(yīng)商:負(fù)責(zé)芯粒間高速互連的接口IP、硅中介層或相關(guān)基板材料的供應(yīng)商,是Chiplet系統(tǒng)高效運(yùn)行的關(guān)鍵。

###

在先進(jìn)制程逼近物理與成本雙重極限的背景下,Chiplet技術(shù)并非簡單的替代方案,而是開啟了一個(gè)以系統(tǒng)級(jí)架構(gòu)和異構(gòu)集成為核心的新創(chuàng)新周期。它正在從前沿技術(shù)走向規(guī)模化應(yīng)用,其發(fā)展不僅將推動(dòng)半導(dǎo)體產(chǎn)業(yè)進(jìn)入下一個(gè)“后摩爾時(shí)代”,也為投資者提供了在產(chǎn)業(yè)變革中捕捉增長動(dòng)能的清晰主線。把握Chiplet產(chǎn)業(yè)鏈的核心價(jià)值環(huán)節(jié),將是未來集成電路領(lǐng)域投資的關(guān)鍵所在。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.028xbl.cn/product/55.html

更新時(shí)間:2026-02-14 03:17:41